### **DEFECT-FREE SEMICONDUCTOR HETEROSTRUCTURE!**

Universally compliant engineered substrates for defect-free heteroepitaxy in the design and fabrication of high-performance devices

Reference: Boucherif - 2023-003

#### Context

Semiconductor-based technologies are present in the modern devices we use every day. This invention is a new process in the field of semiconductor wafers and substrates, i.e. the creation of a "compliant" substrate, without defects, ready to receive the synthesis of high-performance devices.

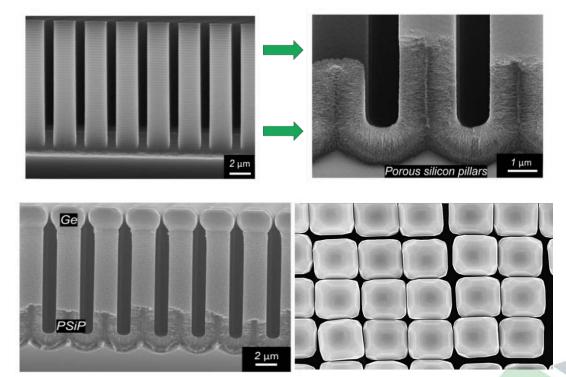

To obtain advanced functionality and high-performance devices (e.g. solar cells, lasers, detectors, etc.), semiconductor layers are deposited on the substrates by "epitaxy". Epitaxy is a technique for growing two crystals; heteroepitaxy is the growth of crystals of different chemical lattices. Unfortunately, heteroepitaxy leads to the genesis of crystal defects that significantly affect device performance. It is therefore necessary to develop a method to eliminate the occurrence of these defects. In addition, to reduce the cost of devices designed with these materials, it's necessary to integrate them on silicon (inexpensive compared to other substrates). An example of such a semiconductor heterostructure is the silicon-germanium (Si-Ge) substrate, as shown in Figure 1.

Figure 1 – Scanning Electron Microscope images: Top left: Deep patterning of the Silicon (Si) substrate using the Bosch process, resulting in micrometer-scale Si pillars. Top right: Electrochemical porosification. Bottom left: Germanium (Ge) deposited by epitaxy. Bottom right: No defects on the pillars, regardless of thickness. PSiP: Porous Silicon Pillars. Source: Université de Sherbrooke.

Further details available in this Nature Communications article: « Defect free strain relaxation of microcrystals on mesoporous patterned Silicon – https://www.nature.com/articles/s41467-022-34288-4.

200-35, Radisson Sherbrooke QC J1L 1E2 CANADA t **819 821-7961**

## Description

The invention consists of modifying the silicon substrate so that it prevents the nucleation of defects; a combination of existing methods: microstructured substrate, porosification and graduated diffusion. The combination of these processes makes it possible, for the first time, to produce heteroepitaxy without defects. The invention therefore makes it possible to grow thick layers without cracks and without crystalline defects, despite the lattice mismatch between the layers and the substrate, which remains to this day the "Holy Grail" of this field.

This technology thus makes it possible to significantly increase device performance while offering direct integration onto a standard Si platform. It consists of creating spatially localizable porous microstructures on a standard silicon substrate. The elasticity of porous silicon microstructures increases greatly with porosity. We then exploited this property to accommodate the difference in lattice parameters between the substrate and the epitaxial layers and succeeded in obtaining defect-free Ge microstructures on silicon.

## **Applications**

Ο

Better costs and performance:

- Photon emitters and detectors operating in UV, visual and IR; integrated photonic circuits on Si; power electronics; solar cells; LIDAR; telecommunication by optical fibers; others.

- Some targeted global markets

- Lasers, diodes, single photon (quantum) emitters, transistors, solar cells.

- E.g.: Multi-junction solar cells (the most efficient) US\$5.439 billion market in 2022, with a CAGR of 6.3% according to Markets & Markets.

- Silicon photonics for telecommunications and data communications:

Market of US\$1.950 billion in 2023, with a CAGR of 23.4%!

- Large volume photodetectors such as LIDAR for the automotive market and cell phones.

- Targeted companies

- Umicore, Teledyne Dalsa, Excelitas, Laser Components, Samsung, Meta, 5N Plus, SOITEC, STMicroelectronics, GaN Systems.

#### **Advantages**

- This method meets all the following criteria, a first!

- o Compliance

- o Adaptable settings

- Mechanical/handling resistance

- o Good crystal structure

- High temperature stability

- Simplicity of implementation

- o Transferable to large surface areas

- Resolution of the fundamental problems of hetero-epitaxy: possibility of cleanly integrating III-V materials on silicon.

- The structure of the pillars can be adjusted to maximize the performance of the desired devices.

- Industrial compatibility / existing assembly lines.

- Permits making devices that were previously impossible to make, e.g. lasers or sensors on silicon.

- Enables more efficient and lower cost devices.

- This method applies to all silicon semiconductor technologies; Si is 6 times cheaper than Ge! E.g. the price of the substrate for a Ge solar cell represents 50% of the total price. Integration on Si considerably reduces the price of the devices.

#### **Keywords**

Compliant substrate, deeply patterned substrate, porous substrate, porosification, porous material, defect-free heteroepitaxy, diffusion, infiltration, opotoelectronics.

200-35, Radisson Sherbrooke QC J1L 1E2 CANADA t **819 821-7961**

### **Technology Readiness Level (TRL)**

#### TRL 3-4

- Experimental demonstration on silicon with germanium; see article above.

- We believe that such a compliant template paves the way towards the potential synthesis of defect-free heterostructures including the direct growth of various materials such as GaAs, InP, and GaN.

# **Intellectual Property**

- Patent applications filed.

### Seeking

- Development partners

- Commercial partners

- Investments

- Licenses

- Start-up

#### **Inventor Contact**

Professeur Abderrouf Boucherif Abderraouf.Boucherif@USherbrooke.ca

#### TransferTech Sherbrooke Contact

François Nadeau <u>f.nadeau@transfertech.ca</u> 873 339-2028 www.transfertech.ca

200-35, Radisson Sherbrooke QC J1L 1E2 CANADA t **819 821-7961**

015 021 750